Writing safe Verilog

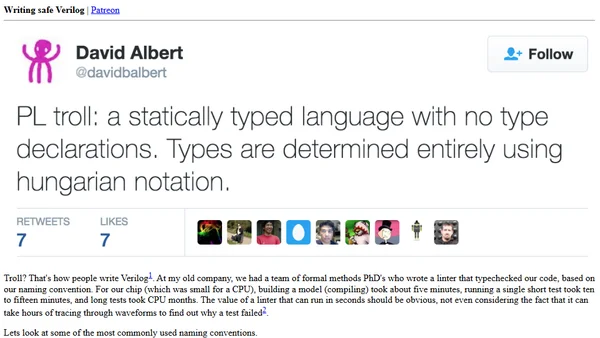

Read OriginalThis article discusses critical practices for writing safe Verilog code, focusing on naming conventions for pipeline stages and clock domains. It explains how proper naming helps prevent common hardware errors like timing failures, metastability, and excessive power consumption that can damage chips. The author draws from professional experience to highlight the importance of these practices in avoiding costly debugging sessions and potential hardware meltdowns.

Comments

No comments yet

Be the first to share your thoughts!

Browser Extension

Get instant access to AllDevBlogs from your browser

Top of the Week

No top articles yet